# **CA-SpaceNet: Counterfactual Analysis for 6D Pose Estimation in Space**

Shunli Wang<sup>1,2†</sup>, Shuaibing Wang<sup>1,2†</sup>, Bo Jiao<sup>1,2</sup>, Dingkang Yang<sup>1,2</sup>, Liuzhen Su<sup>1,2</sup>, Peng Zhai<sup>1,2</sup>, Chixiao Chen<sup>1,2\*</sup>, Lihua Zhang<sup>1,2,3,4\*</sup>

Academy for Engineering & Technology, Fudan University<sup>1</sup> Engineering Research Center of AI and Robotics, Ministry of Education, China<sup>2</sup>

Jilin Provincial Key Laboratory of Intelligence Science & Engineering, China<sup>3</sup>

Artifical Intelligence and Unmanned Systems Engineering Research Center of Jilin Province, China<sup>4</sup>

**Code:** <u>https://shunli-wang.github.io/</u>

# Experiments

**Quantitative Analysis on the Swisscube and SPEED Datasets**

Comparison with SOTAs on Swisscube.

| Method           | Near ↑ | Medium ↑ | Far ↑ | All ↑ |

|------------------|--------|----------|-------|-------|

| SegDriven [39]   | 41.1   | 22.9     | 7.1   | 21.8  |

| SegDriven-Z [39] | 52.6   | 45.4     | 29.4  | 43.2  |

| DLR [5]          | 63.8   | 47.8     | 28.9  | 46.8  |

| WDR [4]          | 65.2   | 48.7     | 31.9  | 47.9  |

| WDR* [4]         | 92.37  | 84.16    | 61.27 | 78.78 |

| CA-SpaceNet      | 91.01  | 86.32    | 61.72 | 79.39 |

Comparison with SOTAs on SPEED.

| Method               | $\mathbf{e}_q + \mathbf{e}_t \downarrow$ |

|----------------------|------------------------------------------|

| SLAB Baseline [3]    | 0.0626                                   |

| pedro-fairspace [42] | 0.0571                                   |

| WDR [4]              | 0.0180                                   |

| WDR* [4]             | 0.0400                                   |

| CA-SpaceNet          | 0.0385                                   |

(a) SpaceX Crew-2 Docking Mission

#### (b) Preview of the ClearSpace-1

Practical applications of the 6D pose estimation in many space missions. The complicated background of aerial images will interfere with the stability of the 6D pose estimator.

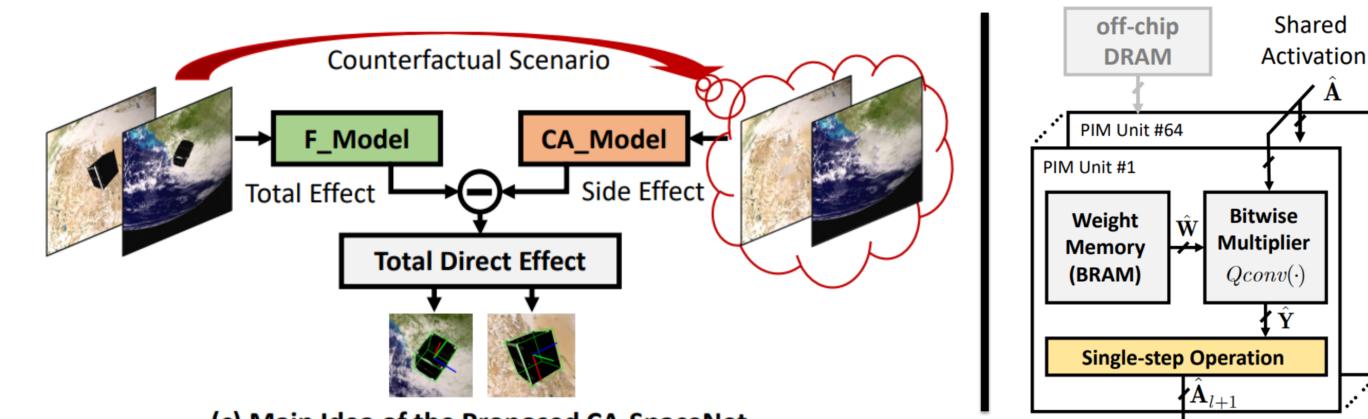

(c) Main Idea of the Proposed CA-SpaceNet

- This paper introduces counterfactual analysis to the 6D pose estimation task in space and proposes the CA-SpaceNet framework.

- We quantize the CA-SpaceNet into a low-bit-width model and deploy a part of the quantized network into a Processing-In-Memory chip on FPGA.

Results on 3 different quantization modes of 8bit and 3-bit CA-SpaceNet on SwissCube.

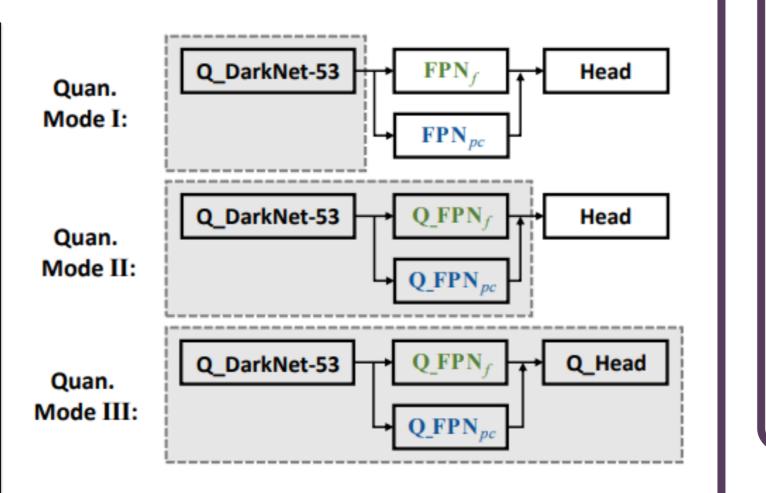

| #Bits | Quan. Mode | ADI-0.1d ↑ | OPs & FLOPs                  | Perc.(%) |

|-------|------------|------------|------------------------------|----------|

|       | I          | 76.21      | 36.91 GOPs +<br>33.79 GFLOPs | 52.21    |

| 8     | Π          | 75.04      | 44.51 GOPs +<br>26.19 GFLOPs | 62.96    |

|       | III        | 74.65      | 70.47 GOPs +<br>0.23 GFLOPs  | 99.67    |

| 3     | Ι          | 75.10      | 36.91 GOPs +<br>33.79 GFLOPs | 52.21    |

|       | Π          | 74.47      | 44.51 GOPs +<br>26.19 GFLOPs | 62.96    |

|       | III        | 68.68      | 70.47 GOPs +<br>0.23 GFLOPs  | 99.67    |

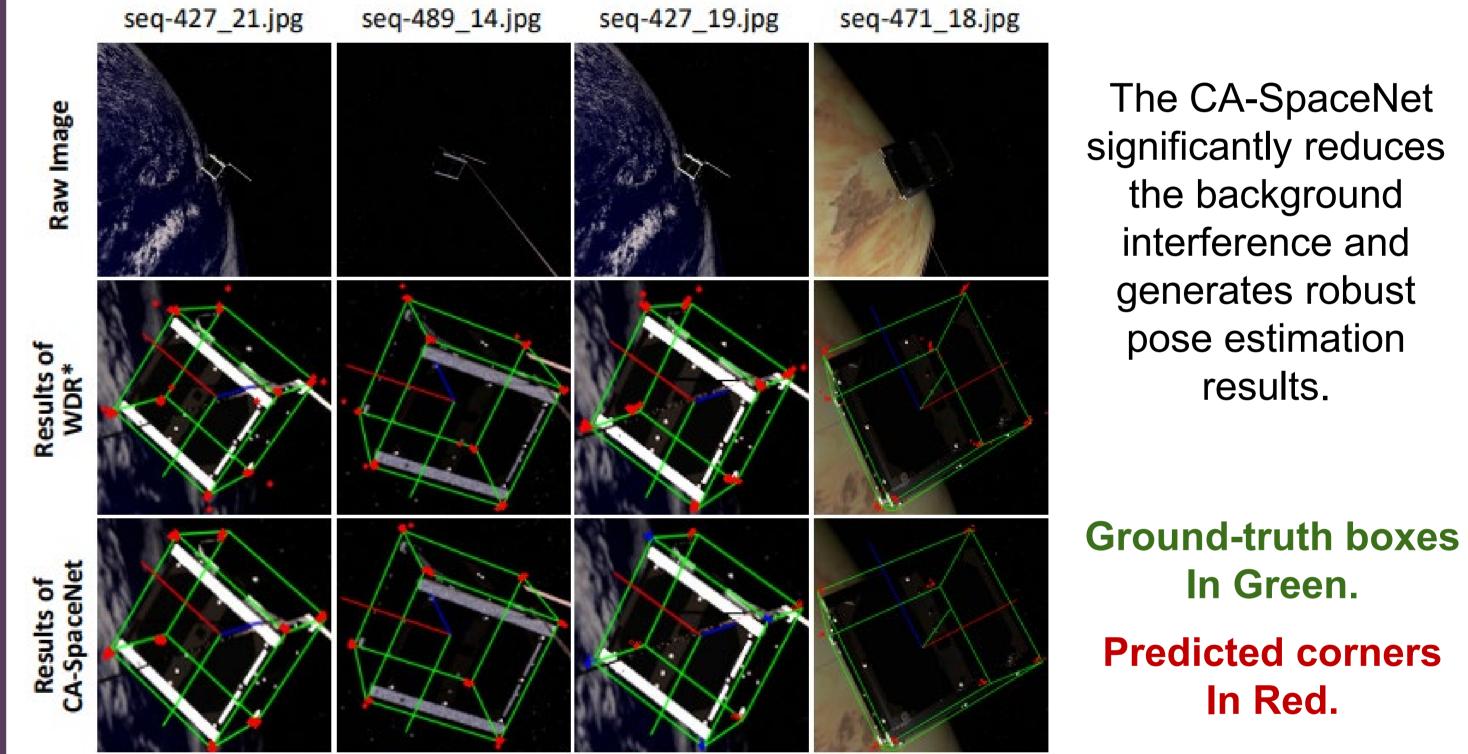

#### Visualization on Swisscube

Summary of #parameters and storage size.

| Format | #Para.  | Model Size | Stor. Saving (%) ↑ |

|--------|---------|------------|--------------------|

| FP32   | 51.29 M | 205.17 MB  | 0.00               |

| 8-bit  | 51.29 M | 51.29 MB   | 75.00              |

| 3-bit  | 51.29 M | 19.23 MB   | 90.63              |

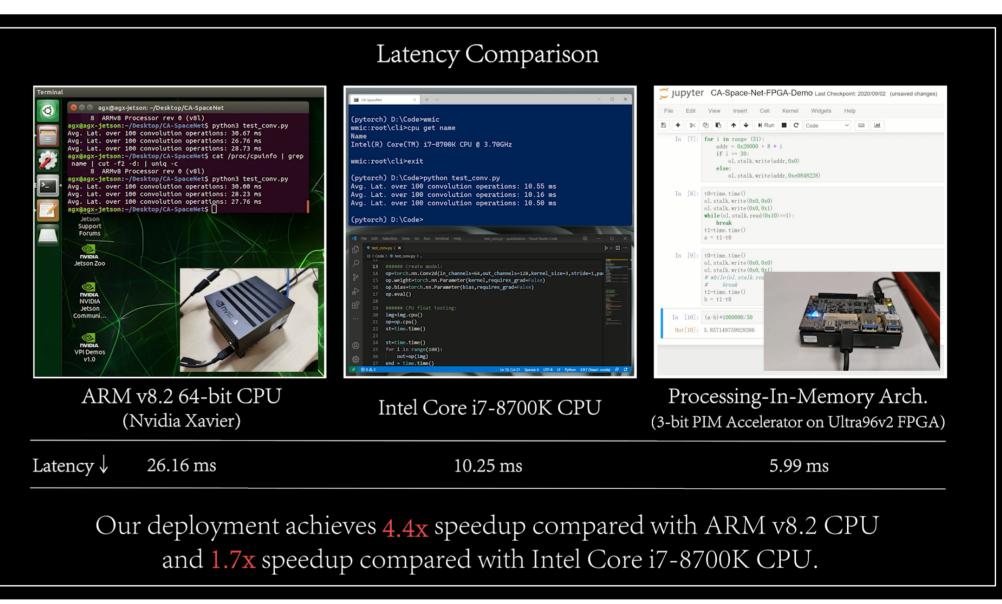

Measured latency on different hardware

| Device                                                         | Latency (ms) $\downarrow$ |  |

|----------------------------------------------------------------|---------------------------|--|

| ARM v8.2 64-bit CPU (Nvidia Xavier)<br>Intel Core i7-8700K CPU | 26.16<br>10.25            |  |

| PIM Arch. on Ultra96v2 FPGA                                    | 5.99                      |  |

The CA-SpaceNet significantly reduces the background interference and generates robust pose estimation results.

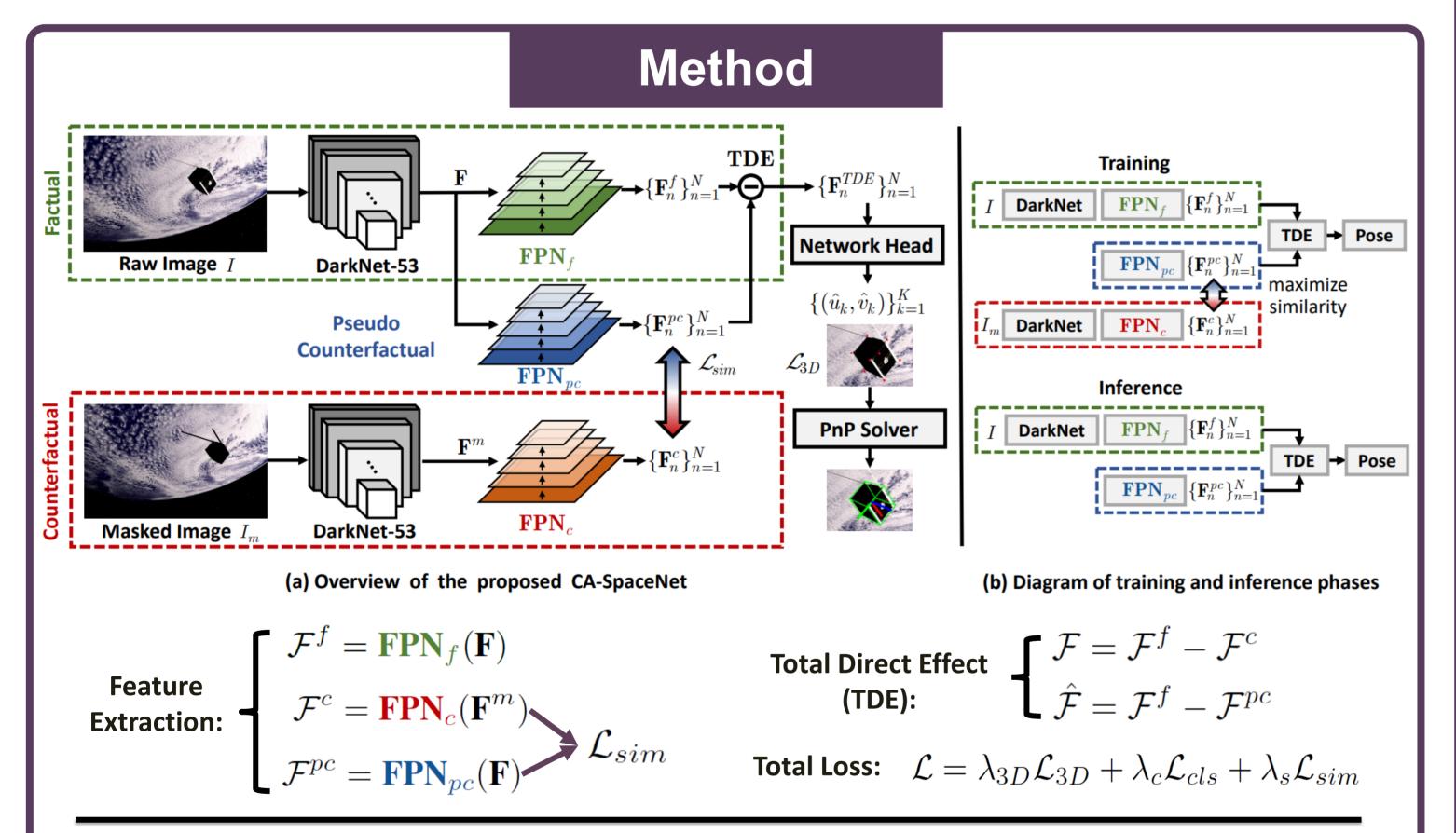

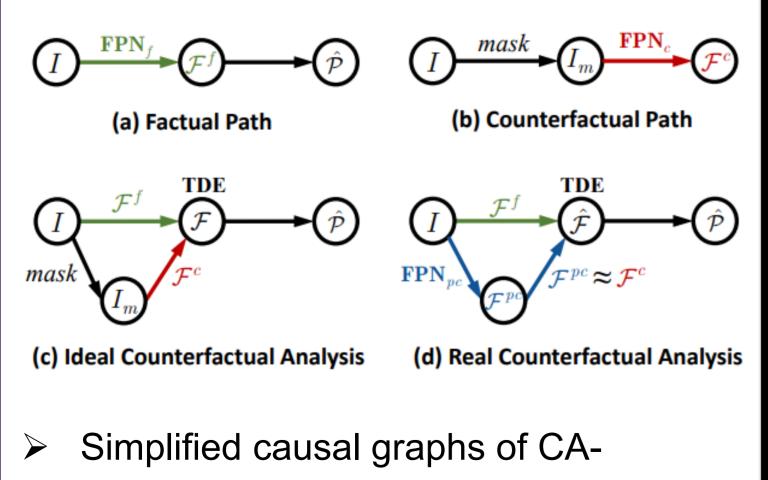

- **Factual Path:** The factual path is designed to simulate the phenomenon of background interference.

- **<u>Counterfactual Path</u>**: The idea of counterfactual analysis is to imagine a non existent path, that is, to study the effect under the *What If* scenario.

- **Pseudo Counterfactual Path**: As its name implies, pseudo means that this path is a fake path, which aims to imitate the counterfactual path.

Measured Latency Comparison: PIM v.s. CPU

In Green.

In Red.

Our real deployment of the PIM Architecture on the Ultra96v2 FPGA achieves:

**4.4x** speedup than ARM v8.2 CPU, **1.7x** speedup than Intel Core i7-8700K CPU.

### **CA Module & Quantization**

### Conclusion

- SpaceNet in four situation.

- These causal graphs consist of four types of nodes: image node, feature node, TDE node, and pose results node.

- Three quantization modes are set up:

- only quantizing the backbone,

- quantizing the backbone and FPN,

- quantizing all modules.

- In this paper, We propose CA-SpaceNet based on counterfactual analysis to weaken the interference of background from the mixed features.

- Experimental results on SwissCube and SPEED datasets show that the proposed framework achieves robust performance.

- Further, we quantize the CA-SpaceNet into 3-bit and 8-bit and deploy part of the quantized network to a neural network accelerator on FPGA.

## Acknowledgements

This work is supported by Shanghai Municipal Science and Technology Major Project (2021S) HZDZX0103) and NSFC Grant (61974033).

# Contact

Shunli Wang slwang19@fudan.edu.cn Lihua Zhang\* lihuazhang@fudan.edu.cn